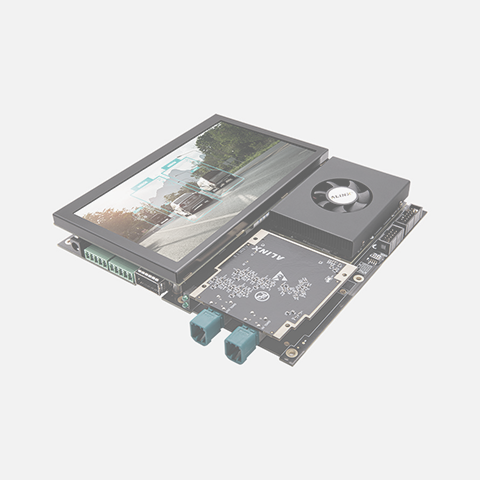

YunSDR Y750Neo

EIC Product Code:

YunSDR Y750Neo is the latest flagship model of the 7 series, targeting the emerging 7.2GHz frequency band of 5G and WiFi7. It adopts high-performance RF front-end and third-generation Xilinx Zynq UltraScale+RFSoC construction, meeting the verification and development of next-generation wireless communication standards. As a high-performance multi-channel software defined radio platform, the frequency range is from 1MHz to 8GHz, supporting four independent transmission and reception channels, with an instantaneous bandwidth of up to 400MHz. The sampling rate of high-speed ADC can reach up to 5GSPS with an accuracy of 14 bits, while the sampling rate of high-speed DAC can reach up to 9.85GSPS with an accuracy of 14 bits. The data transmission interface adopts 100G optical fiber, and real-time interaction with the upper computer is achieved through a PCIe3.0x16 programmable FPGA front-end card. In addition, the device provides standard control and debugging interfaces, including USB-JAG, 10/100/1000M Ethernet, TF card, USB3.0, etc. The start mode switch can flexibly configure various start modes, with 12V DC power supply.

Covering the frequency range of 1MHz-8GHz; Four channel real-time transmission and reception bandwidth of 400MHz; 2x100G high-speed data transmission interface, standard PCIe 3.0 front card, and additional massive FPGA logic resources provided; Ready to use software toolkit, supporting RF acquisition, recording, and playback; Rich secondary development API resources, cross platform support for MATLAB, Python, C #, C/C++, etc; Integrated with the open-source GNU Radio development environment, it can directly run open-source 4G and 5G protocol stacks.

Main features and interfaces:

High performance, channel density, and high integration

Two development modes: standalone mode (embedded) or host mode (100G to PCIe streaming mode)

1 MHz to 8GHz frequency range (expandable to millimeter wave frequency band)

Real time bandwidth 400MHz mode

4-channel transmission, 4-channel reception

Xilinx Zynq-Ultrascale+ ZU47DR RFSoC

14 bit ADC, 14 bit DAC

IQ sampling clock 500MSP, supporting 983.04MSPS and 960MSPS simultaneously

Four core ARM Cortex-A53 processor, with a maximum clock speed of 1.2 GHz

Four core ARM Cortex-A5 MPCore processor, with a maximum clock speed of 400 MHz

2 x QSFP28 optical ports (supporting 40G/100G Aurora and custom protocols)

Provide PCIe fronthaul acceleration card, PCIe Gen3 x 16 interface, Xilinx Kintex Ultra Scale+KU15P FPGA, 2 QSFP28 optical ports

Gigabit Ethernet RJ45

Reference clock input/output

Trigger signal input/output

Built in GPSDO

FPGA GPIO interface

USB 3.0 Host/Device Interface

Type C USB port serial console, JTAG