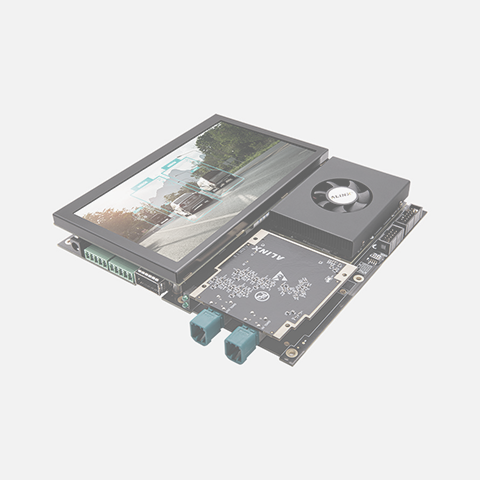

YunSDR Y590 Neo

EIC Product Code:

Y590 Neo integrates a high-performance Zyng SoC FPGA with ultra-large capacity, which can meet the demanding computing requirements of high-performance MIMO communication systems and provide the possibility of deploying large-scale reliable distributed wireless systems. It provides 4 transmit and 4 receive channels in a 1/2-width 19-inch chassis. The RF front end uses the ADRV9026 transceiver, and each channel provides up to 200 MHz instantaneous bandwidth. Through expansion options, it covers the full frequency range from DC to 44 GHz to meet the requirements of 5G FR1 and FR2 bands. The open source GNU Radio hardware driver AP| and Xilinx FPGA HLS development framework reduce the workload of software development and the use of various industry-standard tools. Users can quickly perform prototype verification and reliably deploy various SDR applications, such as 5G prototypes, phased array radars, spectrum monitoring, etc. The Y590 Neo baseband processor uses Xiinx's ZYNQ7100 SOC, which provides a rich set of programmable FPGAs for real-time and low-latency processing as well as dual-core ARM CPU stand-alone operations. Users can deploy applications on the pre-installed Linux embedded operating system, or use high-speed interfaces such as Gigabit Ethernet and 40G optical ports. The Y590 Neo has a flexible reference clock design architecture that supports external PPS or reference clocks, GPS synchronization interfaces, and helps implement large-scale MIMO systems.

- Covering 75MHz~6GHz

- Bandwidth of 200MHz (expandable to 400MHz)

- Programmable baseband ZYNQ SoC 7100 FPGA

- 40G SFP+

- Fully supports 5G/6G system verification

Covering 75MHz~6GHz, bandwidth 200MHz (expandable to 400MHz), programmable baseband ZYNQ SoC 7100 FPGA, 40G SFP+, fully supporting 5G/6G system verification