THE TILE PROVIDES DEVELOPERS WITH THE FOLLOWING CAPABILITIES

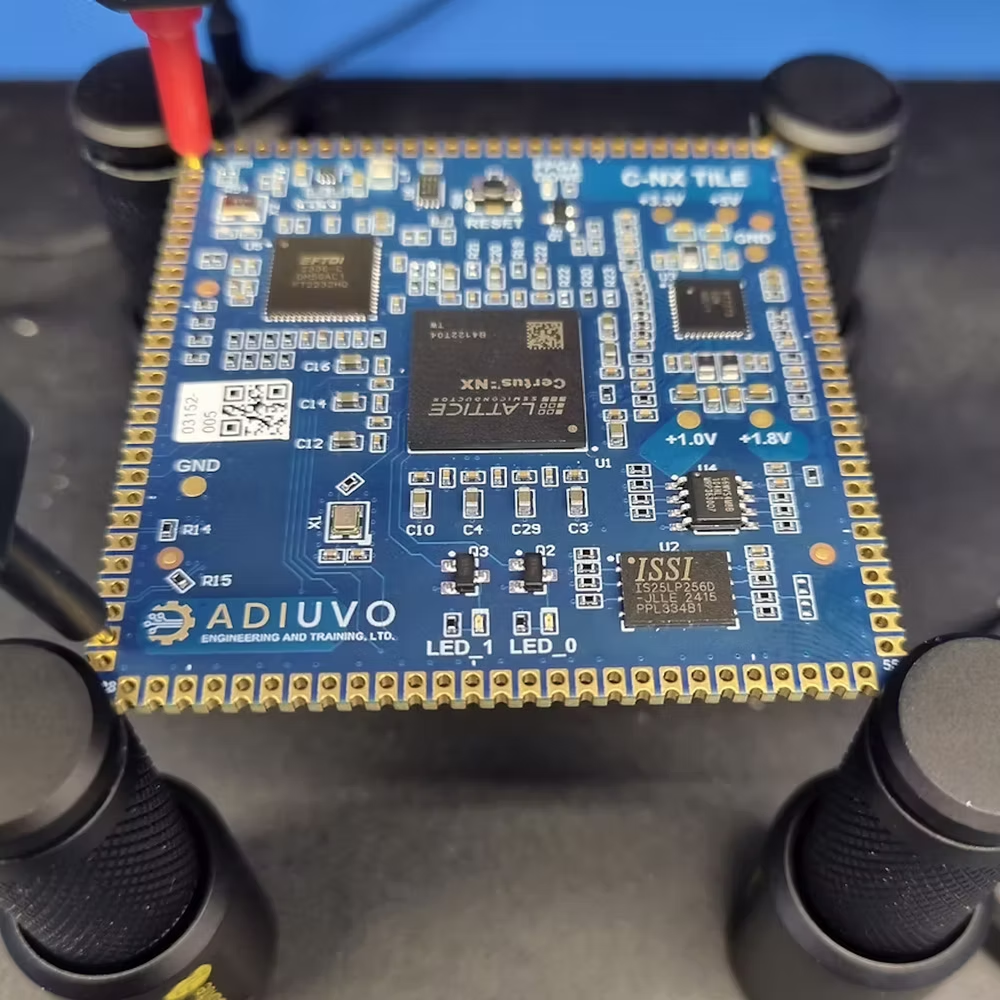

- 59 mm by 59 mm

- Single Supply Voltage 4.5 to 18V

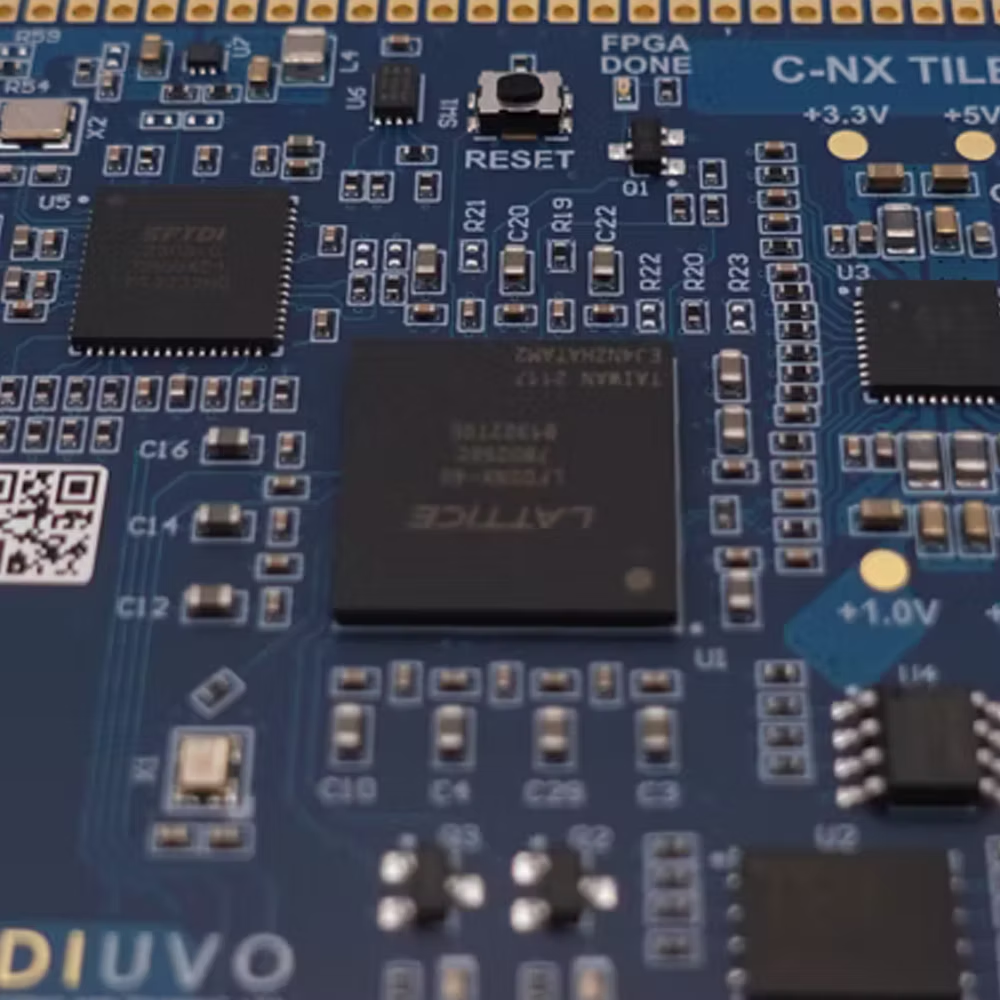

- Onboard UART Debug Interface

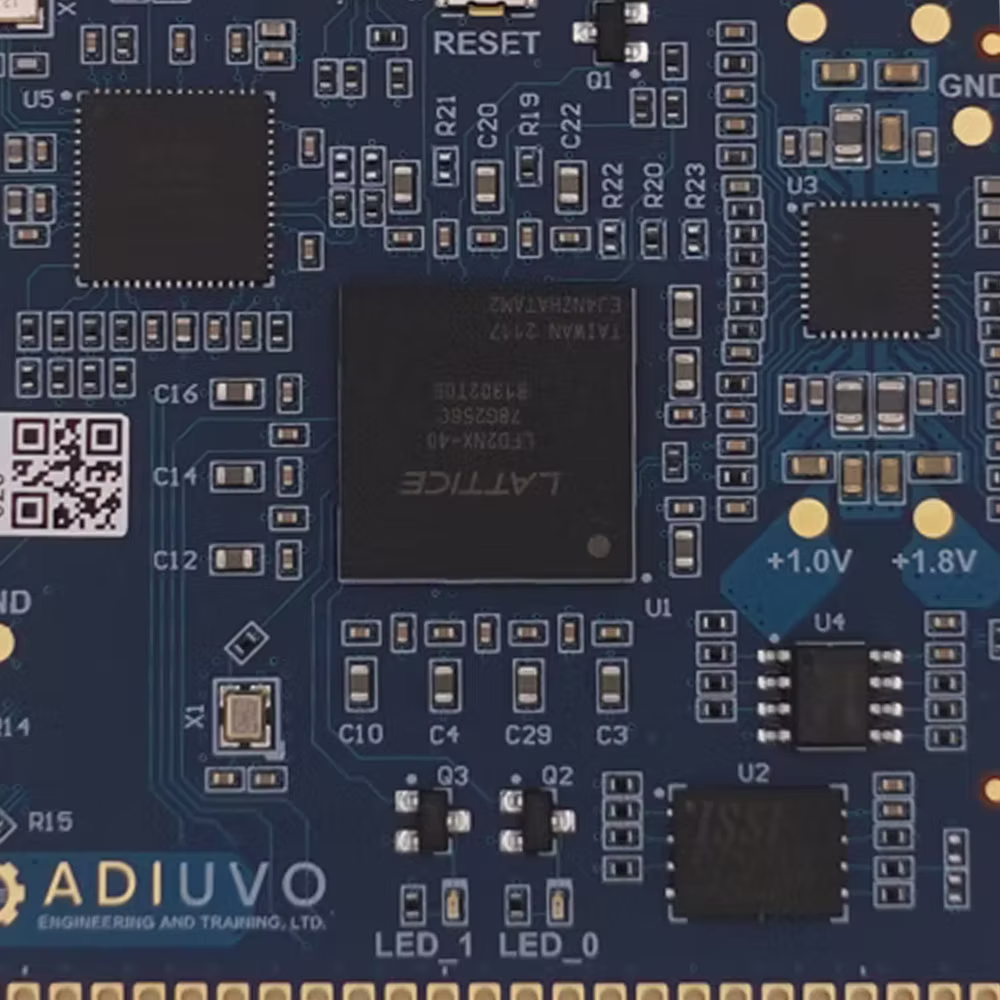

- Lattice Certus™-NX LFD2NX-40

- Configuration Memory 256 Mbit QSPI

- Done LED and Two user LED

- USB JTAG

- USB Connector needed on carrier board

- 100 MHz Oscillator

- Other Global clock pins broken out via IO

- Reset Button

- PSRAM – 32Mbit – Serial RAM connected to the FPGA

- 82 IO including – Power and Ground, JTAG, 32 IO at 3v3, 41 IO configurable voltage (3v3-1.2V and LVDS)